How to estimate sampling clock jitter

Recent advances in ADC design have greatly expanded the available input range so that system designers can remove at least one intermediate frequency stage, thereby reducing cost and power consumption. Special attention must be paid to sampling clocks in undersampling receiver designs because clock jitter can be a major cause of limiting signal-to-noise ratio (SNR) at high input frequencies. This article focuses on how to accurately estimate the jitter of a clock source and how it can be combined with the aperture jitter of the ADC.

Review of the sampling process

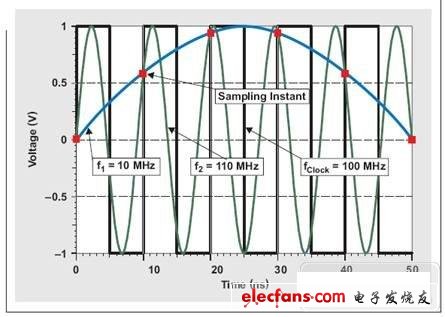

According to the Nyquist-Shannon sampling theorem, if the original input signal is sampled at a rate at least twice its maximum frequency, it can be fully reconstructed. Assuming a sample signal of up to 10MHz is sampled at a rate of 100 MSPS, it doesn't matter whether the signal is in the baseband from 1 to 10 MHz (the first Nyquist region) or undersampled in the higher Nyquist region from 100 to 110 MHz (please See Figure 1).

Figure 1 Two input signals sampled by 100MSPS show the same sample points brought by aliasing

Sampling in higher (second, third, etc.) Nyquist regions is generally referred to as undersampling or subsampling. However, anti-aliasing filtering is required in front of the ADC to sample the ideal Nyquist region while avoiding interference during the reconstruction of the original signal.

Time domain jitter

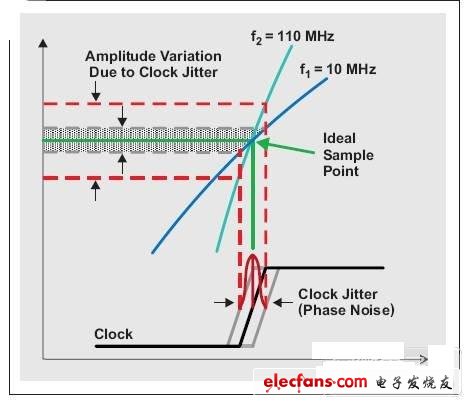

Looking closely at a sample point, you can see how timing changes (clock jitter or clock phase noise) form amplitude changes. Due to the increase in input frequency due to undersampling of high Nyquist regions (eg, f1 = 10 MHz to f2 = 110 MHz), a fixed amount of clock jitter produces a greater amount of amplitude deviation (noise) from the ideal sample point. In addition, Figure 2 shows that the clock signal's own slew rate affects the change in sampling time. The slew rate determines how fast the clock signal passes through the zero crossing. In other words, the slew rate directly affects the trigger threshold of the clock circuit in the ADC.

Figure 2 Clock jitter forms more fast input signal amplitude error

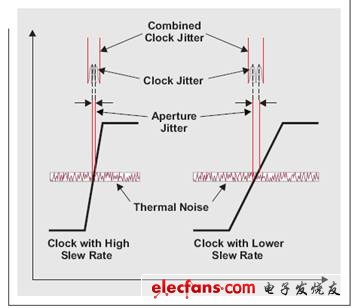

If there is a fixed amount of thermal noise on the ADC's internal clock buffer, the slew rate is also converted to a timing error, which reduces the ADC's inherent window jitter. As shown in Figure 3, window jitter is not related to clock jitter (phase noise), but the two jitter components are combined at the sampling time.

Figure 3 ADC window jitter

Figure 3 also shows that window jitter increases as the slew rate decreases. The slew rate is generally directly dependent on the clock amplitude.

Non-Shielded Control Cable YY CVV LIYY

Low Voltage Control Cables

Standard applied: IEC60227, BS 6500

Rated Voltage: 300/500V 450/750V 0.6/1kV

Others: Fire Cable and other property Low Voltage Power Cable can be available

Applications: Those Control Cables are suitable for fixed installations as connection and inter-connection cables in general machine,production lines.

Non-Shielded Control Cable Yy Cvv Liyy,Non-Shielded Control Cable Yy,Non-Shielded Control Cable Cvv,Non-Shielded Control Cable Liyy

Shenzhen Bendakang Cables Holding Co., Ltd , https://www.bdkcables.com