Interactive set-top boxes and digital TVs have evolved from discrete device architectures to single-chip solutions, which are the result of technological advances in digital LSI manufacturing processes and are an inevitable requirement for minimizing system cost. Set-top boxes for modern single-chip solutions typically integrate modules such as CPU, demultiplexing, audio and video decoding, 2D graphics processing, encoding, and peripheral ports. To save chip area, these separate parts are connected by bus. Improving the performance of the system is usually to improve the speed of the CPU, enhance the processing capability of 2D or even 3D graphics, increase the number of interfaces and categories of peripheral ports, and thus improve the interactive processing capability of the system as a whole. However, since the video demultiplexer and the audio video decoder have strict requirements on real-time access to the data bus, the CPU processing waiting time is increased, and a so-called bus bottleneck is formed. Tests show that the bus bottleneck makes the CPU execution instruction waiting time reach 76%. This way of simply improving CPU performance to overcome the lack of processing power can not improve the cost performance, and improving the bus bottleneck can improve or increase the system interconnection bus. To complete, but this will certainly increase the complexity of interconnecting lines in chip manufacturing, thereby increasing costs.

In addition to the problems caused by the bus bottleneck, with the increasing diversity of access methods and graphics and image processing requirements, the interactive set-top box backed by the telephone line, the narrowband access method of digital TV and limited computing power It is also increasingly unable to meet people's requirements. With the two-way transformation of the wired HFC network and the acceleration of the integration of the telecommunications network and the Internet, the user can add flexible and optional bandwidth access modes such as Cable Modem CM and Ethernet. And the addition of advanced 2D and even 3D advanced graphics processing has become an important aspect of set-top box applications. Dual CPU solution based on ST40GX1 and STi5514

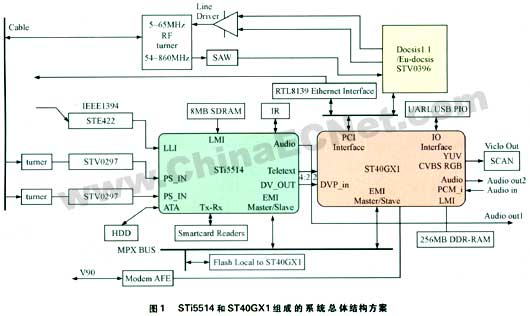

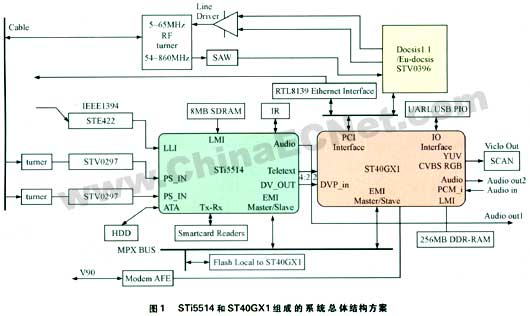

In order to solve the above problems, the design can choose ST's dual-processor solution based on STi5514 single-chip decoder and ST40GX1 two-dimensional graphics processor, which avoids bus congestion and decoding caused by peripheral module multiplication. Waiting latency due to real-time requirements. Both the STi5541 and ST40GX1 use high-speed and advanced STBus to interconnect. The former is responsible for real-time hardware demultiplexing, video and audio decoding, and peripheral I/O device control associated with decoding. The latter is responsible for broadband interactive applications and advanced graphics processing. The high-speed data communication between the two is carried out through the MPX (Memory Periheral Exchange) bus and the memory-mapped mailbox (Mailbox), through the MPX bus with a frequency of up to 100 MHz, STi5514 Direct access to up to 256MB of DDR SDRAM storage resources on the ST40GX1.

功能 STi5514 features and interfaces

STi5514 is mainly used to complete the decompression of MPEG-2 video and audio signals. It integrates a MP@ML standard definition video decoding module and a Dolby AC-3/AAC/DTS audio decoding module as well as Video Encoder and Audio DAC modules. The internal 32-bit RISC CPU works at a frequency of 120 Hz. Under the external V.90 hardware Modem, it can be used for narrowband interactive applications over the telephone line, such as video on demand based on telephone line backhaul, low-speed Internet browsing.

Compared with ST's early single-chip decoder STi5512, it has the same features as the general function interface: the instruction and data buffer are doubled, and the three-way TS (Transport Stream) stream input and support are concurrently processed. Multiple descrambling modes (including DVB, DES, ICM, Fast-I), directly support Dolby AC-3/AAC/DTS audio decoding, provide ATAPI hard disk circuit interface, and directly support Ultra-DMA66 high-speed data transfer mode hard disk In order to realize real-time recording of digital TV programs, the video decoding stream can be output in the ITU-R601-656 format data stream or in different analog modes such as composite video signal CVBS, component signals RGB and YUV, and support Teletext decoding output, while providing two pairs. Road SIM card interface. Conducive to the expansion of advanced applications such as bank cards. Since the STi5514 removes the 1394 interface, an external 1394 controller (such as STE422) is required to extend the 1394-based video input.

功能 Functional structure of ST40GX1

ST40GX1 integrates SH-4 32-bit RISC processor core, Gamma 2D image processing, hybrid module and other video circuit interface logic. ST40GX1 is the processing core of interactive application, including system equipment and peripherals: (1) System equipment

The system equipment of the ST40GX1 includes a central processing unit (CPU), a floating point arithmetic unit/addition processing unit (FPU/Mac) for DSP functions, a storage management unit (MMU), and a DMA control module. Among them, the CPU is a 32-bit SuperH RISC, which uses a 2-channel superscalar architecture, clocked at 166M Hz, 16-bit instruction fixed length (Load-Store structure), 8KB direct instruction cache, 16KB direct operand cache, and one On-chip multiplier. The memory supports 4GB of storage space and supports single or multiple virtual memory modes. The page size can be 1KB, 4KB, 64KB or 1MB. In addition, it supports 4-channel full correlation instruction ITLB (Instruction Translation Lookaside Buffer). ), 64-channel fully correlated instruction and operand UTLB, support software-controlled update algorithm and random count update algorithm, which provides a complete hardware platform for the operating system in 32-bit protected mode, general-purpose DMA controller in ST40GX1 Supports 5 channels of data transfer, 4 of which can be used for memory-to-memory or memory-to-peripheral data transfer, and the other is a buffered multi-way composite channel that supports 2D block movement and Linked list operation, the DMA handshake signal and EMI interface signals of the two channels on the chip can also be used for MPX bus operation.

(2) Peripheral interface module

The peripheral interface module of ST40GX1 includes a universal interface module and a video dedicated interface module. The universal interface module includes two full-duplex asynchronous serial communication ports compatible with ST40 series processors, an interrupt controller, and a modulation controller conforming to the IEEE1149 specification. , real-time clock, 4 user-programmable PLLs, configurable parallel I/O ports with 24-bit input and output directions, and two USB host controllers and transceivers conforming to V1.1 specification, Modem analog front-end interface MAFE, two Synchronous serial controllers (SSC0 and SSC1) configurable to support I2C or SPI bus interface standards, Teletext input interfaces, two SmartCard interfaces using asynchronous protocols, and memory mapped mailboxes for communication with external microcontrollers (Mailbox PCI 2.1-compliant PCI interface controller, two audio PCM input interfaces and one PCM output interface; and video dedicated interface and processing module including word video input port and 2D image processor, these two CCIR601 The -656 video output port (DVP0, DVP1) can simultaneously input video data in VCbCr4:2:2 format and load it into local memory. It is also possible to provide external synchronization signal support according to the SAV/EAV protocol for a video without an embedded synchronization signal, and the user can set a video capture window and a sub-window of the active window from the input video image. Digital Encoding (DENC) converts digital video streams into standard analog baseband PAL/SECAM/NTSC signals and RGB and YUV analog component signals. If 32-bit DRAM is used on the LMI, RGB 24-bit digital video streams can be obtained. The 2D image processor (or image block transfer engine) has two 2D DMA image data input sources, which can complete a complete set of powerful processing operations. In addition to the normal 2D graphics acceleration function, different graphic formats can be completed (RGB/ Conversion between YUV, etc., including block fill, block copy, asynchronous composite, color transform, and 2D scaling processing.

System configuration based on STi5514 and ST40GX1

According to the functional characteristics of STi5514 and ST40GX1, Figure 1 shows the overall structure of the system.  |

|---|

å‰ç«¯ Front end decoding part

Since the STi5514 has three channels of TS stream descrambling channels, the dual-channel Turner+STV0297QAM demodulator is used to simultaneously demodulate the DVB-C-based video data transmission streams of two channels, making full use of the hardware descrambling and control processing of the STi5514. The decoding capability enables the picture-in-picture function. Turner can use MicroTune's MT2040 single-chip tuner to save space and cost. In addition, it supports IEEE1394 interface input through an external STE422.

åŽç«¯ Backend decoding part

The back-end decoding is done by the STi5541. The STi5514 completes the memory resources required for channel demodulation, demultiplexing, and decoding through an external 8MB shared SDRAM. The STi5514 shares 16MB of FLASH on the ST40GX1 EMI interface through the MPX bus, through the ATA interface. External hard disk storage to extend VCR applications. The STi5514 decoded video data conforming to the ITU-R601_656 standard is directly input to the DVP0 of the two video input ports of the ST40GX1 through the video output port. The STi5514 sends a 27M Hz pixel clock and sync signal to the ST40GX1 to ensure proper reception of the STi5514 video data.

图形 Graphics processing

When using ST40GX1 to process two-dimensional graphics, ST40GX1 can be used to receive the decoded video stream from STi5514, and after interpolation and color space coordinate transformation, it can perform transparency processing (Alpha blending) and saturation processing on other videos such as web browsing. Gamma Processing) and other composite processing, to form a unified video frame buffer data, encoded by the internal DENC into analog TV can receive the composite video signal CVBS, SVideo or component signals RGB, YUV and other outputs.

Because the ST40GX1 only supports the 3.3V PCI interface, it can expand the 3.3V or 5V PCI slot through Intel's SB21150BC. In the case of 3D image processing, it can also be realized by extrapolating the PCI 3D graphics accelerator card.

网络 Network interface for interactive applications

The hardware part of the interactive application can be done by the ST40GX1 and the corresponding network interface. Considering the bandwidth access mode requirements of the network interface, the ST40GX1 can be used to externally provide the PCI bus interface and integrate high-speed interfaces such as Cable Modem and Ethernet.

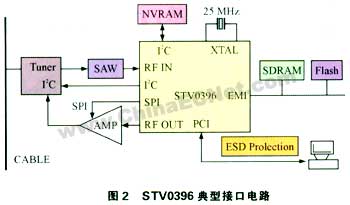

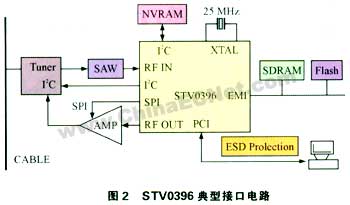

(1) Cable Modem

First select the Cable Modem front-end single-chip interface chip STV0396 that conforms to the Docsis1.1/Euro-docsis1.1 specification as the Cable Modem solution. This part can be designed as a stand-alone PCI card or directly embedded on the motherboard. STV0396 is a highly integrated modem system that includes support for upstream and downstream DOCSIS 1.1 compliant physical layer specification interfaces, Media Access Control (MAC) and powerful 32-bit ST20 RISC processors, PCI, EMI/ An external interface compatible with the ST40GX1 such as MPX. The STV0396 is packaged in a 316-pin GBA package. In addition to the external bidirectional tuner, a surface acoustic wave filter (SAW, upstream line amplifier, and clock) must be added to achieve the CMTS with the cable headend equipment. The communication interface between the two is shown in Figure 2.  |

|---|

(2) Ethernet interface

The RTL8139C-based 3.3V Ethernet chipset can be selected as the interface chip because the chip is highly integrated, widely used in embedded systems, and 10/100M adaptive, self-contained PCI interface, and driven under Linux-like operating system. The program is easy to find and other advantages. The RTL8139 is available in a 128-pin QPF/LQPF package and can be connected to the ST40GX1 via a PCI bus interface.

(3) Support of V.90 software Modem

For the V.90 software Modem support, you can directly use the ST40GX1 Modem front-end interface MAFE to complete. Without using a hardware modem, you can take full advantage of the ST40GX1's processing power to reduce costs.

System startup and communication

The ST40GX1 and STi5514 determine the system startup sequence by configuring the master/slave (initiator/target) mode of the respective MPX bus interface. Here, since the system startup code is located in the ST40GX1 local FLASH, the ST40GX1 is configured as an Initiator to configure the STi5514 as a target. The specific boot sequence is: ST40GX1 first controls the MPX bus and starts first, preventing the STi5514 from using the MPX bus during startup until it completely reads the boot code and initialization from Flash. Then ST40GX1 uses the MPX bus to copy the startup program of the STi5514 and the application code to its own LMI DDR memory. After the copy is completed, the ST40GX1 releases and allows the STi5514 to control the MPX bus. The STi5514 copies its own startup program and application from the ST40GX1 DDR SDRAM. Code, drawing on this, storage sharing between multiple CPUs can be achieved through the MPX bus.

The STi5514 has access to the Mailbox registers on the ST40GX1 via the MPX bus. The Mailbox is fixedly mapped to the base address 0x1B150000 of the ST40GX1 memory space. This register can generate an interrupt signal for both CPUs. Through the Malibox register, the ST40GX1 and STi5514 can realize process synchronization such as process synchronization and message transmission. |