Design of PLC Backplane Bus Protocol Interface Chip Based on Single Chip Microcomputer and CPLD

Abstract: A set of PLC backplane bus protocol interface chip based on CPLD is designed. The protocol chip can distinguish the periodic data and non-periodic data of the backplane bus of PLC. The process of designing state machine, protocol frame controller and FIFO controller through Verilog HDL language is introduced in detail. The test results of stable backplane bus operation at 25MHz verify the feasibility of protocol chip design.

The programmable logic controller (PLC) host supports the expansion module connection through the backplane bus. The backplane bus is a high-speed data path between the PLC host and the I/O expansion module, supporting I/O between the host and the expansion module. Data refresh. The technical level of the backplane bus determines the I/O expansion capability of the PLC product and is the core technology of PLC design and manufacture. At present, PLC mostly uses serial communication technology to realize the backplane bus. The serial bus has few lead wires and low hardware cost. Compared with the parallel bus, it is not easy to be interfered. The serial bus can improve the automation equipment in the harsh factory and industrial environment. reliability. Optional types for serial communication technologies include I2C, UART, SPI, USB, and Ethernet. In general, many of the peripheral components that are the main chip of the PLC integrate themselves. However, the I2C, UART, and SPI peripheral integrated communication speeds of the microcontroller are too slow to meet the communication speed requirements of the backplane bus. Although the communication speed of USB and Ethernet is very fast, because they are all common interfaces, the intervention of the MCU is required in the processing of the communication protocol, and the processing speed of the MCU is slow, so the overall communication speed is still very slow. A large PLC typically collects thousands of I/O data for less than 1 ms. To meet such high-speed communication requirements, a dedicated backplane bus must be designed.

1 Backplane bus works

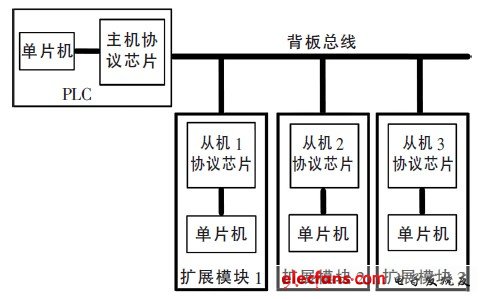

As shown in Figure 1, the data communication process based on the backplane bus is as follows:

(1) The command of the PLC host is sent to the backplane bus through the host protocol chip; (2) The slave protocol chip sends the received command to the MCU of the expansion module, and the MCU of one of the expansion modules responds, and the slave protocol chip is passed. Send the response data to the backplane bus; (3) The host protocol chip receives the response data and sends it to the microcontroller of the PLC host.

Figure 1 Backplane bus communication block diagram

The data sent by the PLC host to the backplane bus can be divided into two categories: one is I/O refresh data, which has periodicity, and the data exchange is very frequent; the other is diagnostic data, which has non-periodicity and less chance of occurrence.

YASKAWA Servo Driver/motor,SGD7S,SGM7,SGMC,SGL

YASKAWA Servo,servo motor,SGD7S,SGM7,SGMC,SGL

Wuxi Trenty Machinery & Equipment Co., Ltd. , https://www.elec-inverter.com