Application of Digital CMOS Camera in Smart Car

introduction

The Freescale Smart Car Competition has been successfully held for 4 sessions. Most of the teams with cameras as the main sensors have chosen analog CCD or analog CMOS cameras. This article introduces the performance characteristics and working methods of the digital CMOS camera MT9M011, gives the application scheme of MT9M011 in the intelligent vehicle control system based on HCSl2 single-chip microcomputer, and analyzes the advantages and disadvantages of the digital camera.

1 Features of CMOS image sensor

CMOS image sensor can integrate pixel array and peripheral support circuits (such as image sensor core, single clock, all sequential logic, programmable functions and A / D converter) on the same chip through CMOS technology. Compared with CCD (Capacitive Coupling Device) image sensors, CMOS image sensors integrate the entire image system on a single chip, which has the advantages of small size, light weight, low power consumption, easy programming, and easy control. At the same time, I2C, SPI and other interfaces are equipped with functions such as exposure time and gain control, which are highly controllable. Therefore, the application of CMOS image sensors has become more and more widespread.

2 MT9M011 performance characteristics and working methods

2.1 Basic parameters of MT9M011

MT9M011 is a 1.3-megapixel digital CMOS camera with three primary colors of RGB introduced by MierON, with programmable control and digital signal output functions. The output is in Bayer color format, the image size is 4.6 mm & TImes; 3.7 mm, the pixel size is 3.6 μm & TImes; 3.6 μm, the maximum resolution is 1 280 & TImes; ; The A / D conversion accuracy is 10 bits, the maximum signal-to-noise ratio is 44 dB, and the power consumption is 129 mW in the highest resolution mode.

The output of MT9M011 is a progressive scan digital signal, and the analog video signal is sampled and quantized by the built-in 10-bit ADC to output a 10-bit data stream synchronously. At the same time, MT9M011 also provides pixel clock (PIXCLK), line valid signal (LVAL), frame valid signal (FVAL), and the I2C protocol pins SCLK and SDAT required to configure MT9M011.

2. 2 MT9M011 programming function

MT9M011 has 25 registers, involving all aspects of the camera, read and write through the serial bus timing compatible with I2C. Combined with the application of smart car competition, the following registers are mainly introduced:

â‘ Row start register (Ox01) and column start register (Ox02). These two registers determine the starting point coordinates of the output image. Using these two registers, software can adjust the overall position of the image collected by the camera.

â‘¡ Row width register (0x03) and column width register (Ox04). A major feature of MT9M011 is that the image size of the output data can be adjusted arbitrarily. Through these two registers, an appropriate image range can be set for the current application environment (ie, the track).

â‘¢ Exposure time register (Ox09). The value of this register determines the photosensitive time of the photosensitive component when the camera collects a frame of image. By adjusting the size of this register value, the imaging quality of the image can be directly adjusted.

â‘£Data read mode register (Ox20). This register can reduce the output row data and column data to 1/2 or 1/4, and can also make the output image mirror symmetrical.

⑤Gain setting register. It also contains 5 registers: Greenl component gain setting register (Ox2B), Blue component gain setting register (Ox2C), Red component gain setting register (Ox2D), Green2 component gain setting register (Ox2E) and global gain setting register (Ox2F). Since the RGB components show different values ​​for the same light source, the values ​​of the first 4 registers need to be adjusted for different light sources, which is also the biggest disadvantage of this camera.

2. 3 MT9M011 digital image output

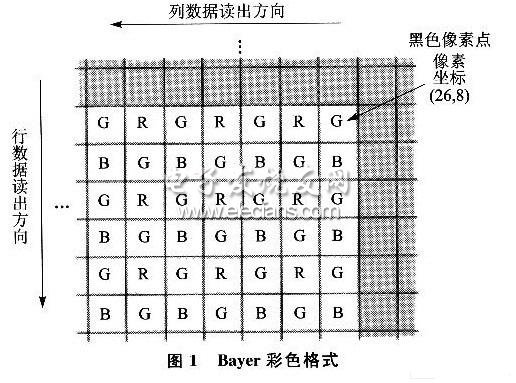

2.3.1 Bayer color format output

The output of MT9M011 is Bayer color pattern (Bayer color pattern). This output format directly outputs the reserved primary color analog level values ​​corresponding to each pixel on the filter array, and outputs them in sequence after A / D conversion. Figure 1 shows the local pixel lattice corresponding to this output format. Among them, the black pixel is the first point to output valid data.

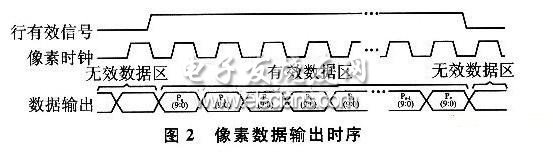

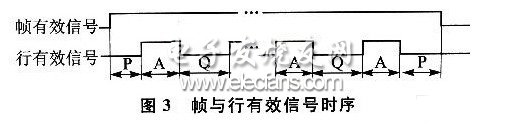

2.3.2 Output signal timing of MT9M011

Pixel data output timing and frame and line valid signal timing are shown in Figure 2 and Figure 3, respectively. The pixel clock is the same frequency as the main clock. The frame valid signal changes from low level to high level when the output of one frame starts, and changes from high level to low level when the output of one frame ends. When data output is valid, it changes from low level to high level, and after one line of data output is completed, it changes from high level to low level. According to the output signal timing of MT9M0ll, the whole frame image can be collected correctly. In FIG. 3, P is a frame blanking area, A is a valid data area, and Q is a line blanking area.

3 Application of MT9M011 in intelligent car control system

3.1 Hardware design

The level of MT9M011 is 3.3 V, and the I / O level of the HCSl2 single-chip system is 5 V, so the level of the camera output data needs to be raised to 5V through a level conversion chip. Combining the timing relationship of the output signal of MT9M011 and the characteristics of HCSl2 MCU, this paper uses the ECT module of HCSl2 to extract the rising edge of the frame effective signal of MT9M011, and uses the common I / O function of the corresponding pin of the ECT module to collect the rising edge of the effective signal of the line. The data output signal of MT9M011 has 10 bits. In view of the relatively simple track environment, only the high 8 bits are intercepted as the camera signal output, which can not only ensure the image resolution, but also save the storage space of HCSl2. HCSl2 one-chip computer has a standard I2C module, use this module directly to connect with SCLK and SDAT of MT9M011.

3.2 Software design

3. 2. 1 HCSl2 one-chip computer I2C module disposition

The HCSl2 single-chip microcomputer provides a standard I2C module. The SCLK pin can generate multiple clock frequencies, support the master-slave mode, and have multiple flag bits for query. The following work needs to be completed when initializing the I2C module:

â‘ Set the IBFD register so that the generated SCLK signal can configure the MT9M011 normally;

â‘¡ Set the IBEN register bit to enable the I2C module;

â‘¢ Set IBCR, determine the I2C module's master and slave modes, receiving and sending modes, and whether to enable the interrupt function.

Guangzhou Yunge Tianhong Electronic Technology Co., Ltd , http://www.e-cigaretteyfactory.com